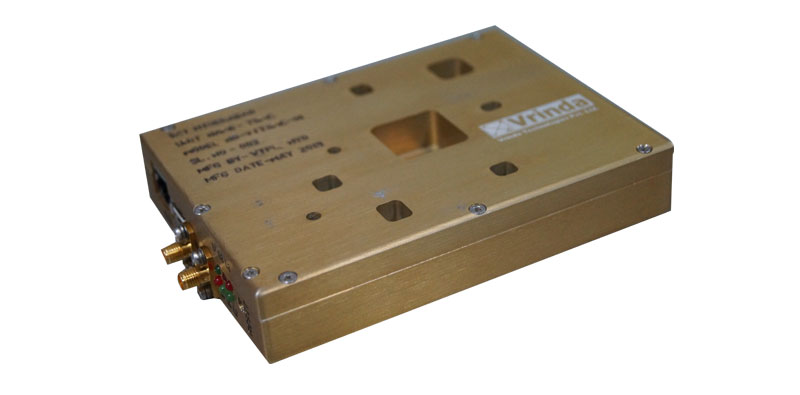

Timing synchronization module is a muti-featured, digitally-controlled solution in miniature size with variable data rate bit synchronizer and de-commutator. It is a key component in telemetry systems for timing and symbol recovery. The unit has the software and hardware infrastructure to perform input signal conditioning, bit synchronization, data reconstruction and clock generation. Apart from the FPGA on board, it has a controller to interface with additional memory and communication modules.

Features:

| FPGA | One SPARTAN6 XC6SLX100T-3FGG656I |

| ARM controller | LPC3250 |

| ADC | 1 Channel (400MSPS) |

| DAC | 1/2 Channels (1GSPS/500 MSPS) |

| Memory | SDRAM(256Mb),FLASH(2Gb),SRAM(16Mb) |

| Communication | USB, Ethernet, RS232, RS422 |

| User IOs | 8 channel isolated DOs, 18 LVTTL |

| OS | Linux 2.6 |

| FUNCTIONAL FEATURES | |

| Bit Rate | Up to 10 Mbps Programmable |

| Words/Frame | Programmable |

| No of sync bytes | Programmable |

| Input Codes | BI-phase & NRZ |

| Sync Threshold | 0dB |

| Loop bandwidth | 0.1 to 3.3% |

| OTHERS | |

| Power Supply | 28V±10% |

| Dimensions | 135mm x 100mm X 25mm size |

| Temperature Range | -40°C to 85°C |