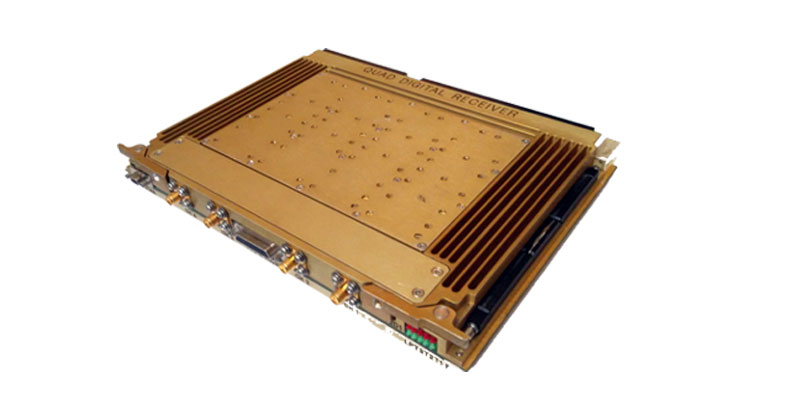

The VPX QDR Board is based on Texas Instrument’s Ultra High speed, Low Power, High Performance10 bit ADC and Xilinx 7 series FPGA's with the 6U VPX form factor. The Board is connected throughVPX backplane with 6U VPX Chassis with a wide range of connectivity. The QuadDigital Receiverhardware accepts 4 IF inputs in the frequency range of 750-1250MHz (IBW:500MHz) / 980-1020 MHz(IBW: 40MHz) / 140-180 MHz (IBW: 40MHz) and processes thesampled data in real time. The results are fed as an output through a 51 pin ‘D’ Connector andalso through VPX backplane. It also supportsSerial Rapid IO’s, Gigabit Ethernet, LVDS andLVTTL Interfaces for Data Transfer. It has dedicated256MB DDR2 memory, Serial EEPROM and 128MB Flash Memory to run the application and processdata.

Features:

| ADC | Four (1.5/3 GSPS) |

| FPGA's | Two Xilinx Virtex 7 XC7VX485T series FPGA One Xilinx Artix 7 XC7A200T series FPGA |

| FPGA Memory | 64MB Configuration PROM for Virtex 7 32MB Configuration PROM for Artix 7 128KB Serial EEPROM for Each FPGA 128MB Parallel Flash Memory for Artix 7 FPGA 256MB DDR2 SDRAM for Artix 7 FPGA |

| sRIO operating @3.125Gbps | x4 Port from Artix 7 FPGA to backplane x1 Port each from Virtex 7 FPGA's to Backplane x4 Port between Virtex 7 FPGA's x2 Port each from Virtex 7 FPGA's to Artix 7 FPGA |

| Serial Ports | One RS232 serial port from Artix 7 FPGA to 51 pin uDConnector |

| Ethernet Ports | One Gigabit Ethernet interface (10/100/1000Mbps) fortransmitting data to external world through Artix 7 FPGA |

| I/O Interfaces | 64 LVTTL signals from Artix 7 FPGA to VPX Backplane 6 LVDS pairs from Virtex 7 FPGA's to VPX Backplane 46 TTL Signals from Artix 7 FPGA to 51 pin uD Connector |

| Form Factor | 6U VPX |

| Temperature range | Industrial Grade |